Summary

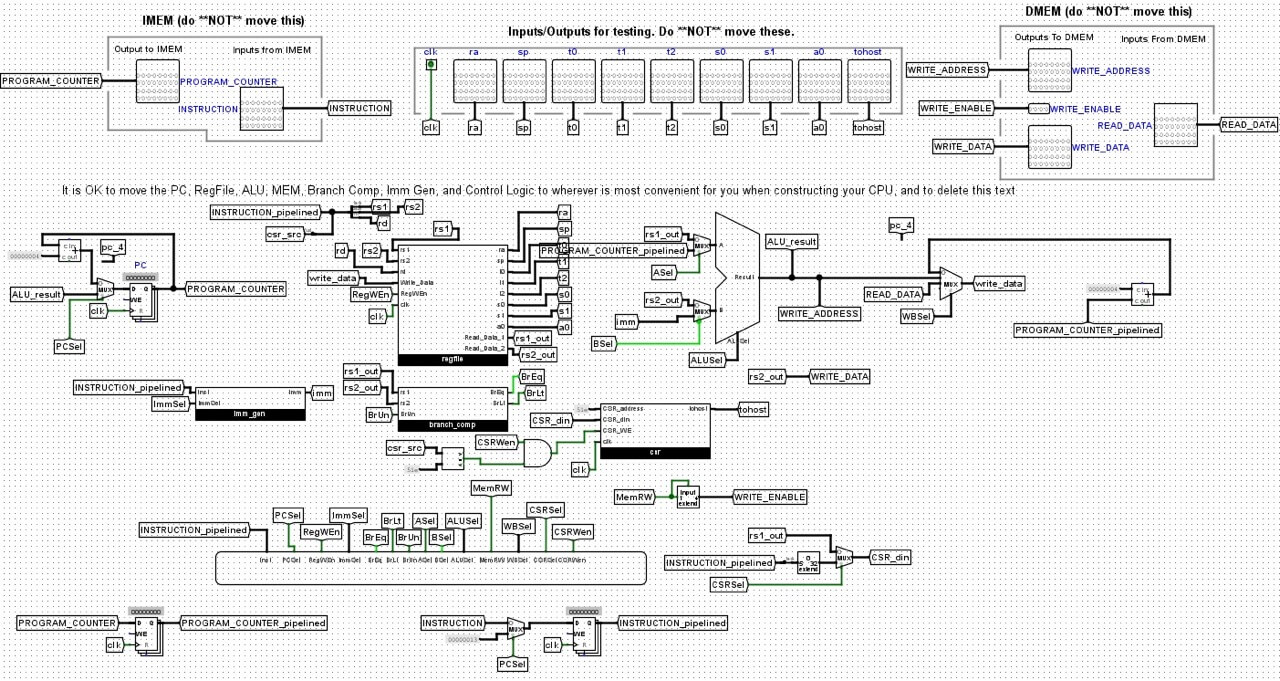

The CPU is designed and created from scratch using Logisim and supports the entire RISC-V ISA. A very insightful learning experience.

The two stages of the pipeline are:

1. Instruction Fetch: An instruction is fetched from the instruction memory.

2. Execute: The instruction is decoded, executed, and committed (written back). This is a combination of the remaining four stages of a normal five-stage RISC-V pipeline (ID, EX, MEM and WB).